# DI2S

## **COMPANY OVERVIEW**

Digital Core Design is a leading IP Core provider and a System-on-Chip design house. The company was founded in 1999 and since the very beginning has been focused on IP Core architecture improvements. Our innovative, silicon proven solutions have been employed by over 300 customers and with more than 500 hundred licenses sold to companies like Intel, Siemens, Philips, General Electric, Sony and Toyota. Based on more than 70 different architectures, starting from serial interfaces to advanced microcontrollers and SoCs, we are designing solutions tailored to your needs.

# IP CORE OVERVIEW

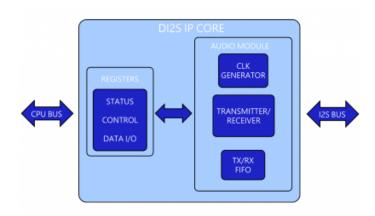

DI2S is a **universal solution** which provides an interface between a microprocessor and **I**<sup>2</sup>S, **left/right justified modes**, **PCM**, **TDM audio protocol codec**. Thanks to **flexible configuration** it can work as a **receiver**, **transmitter in master or slave mode**, with **configurable channel length** or **sample size**. Additionally, number of audio blocks can be adjusted according to specific project needs.

## **KEY FEATURES**

- Configurable number of independent audio modules with their respective FIFO

- Configurable TX/RX mode of each audio module

- Configurable master/slave mode support of each audio module

- Flexible I2S, LSB/MSB (right/left) justified, DSP, TDM modes support

- Configurable sample size (8, 10, 16, 20, 24, 32 bit)

- Configurable number of samples per frame (1 to 16)

- Configurable FIFO depth

- Flexible FIFO threshold interrupt control

- FIFO Underrun/overrun interrupt

- Inter modules clock synchronization

#### **DELIVERABLES**

- Source code:

- VERILOG Source Code

- · VERILOG test bench environment

- Active-HDL automatic simulation macros

- ModelSim automatic simulation macros

- Tests with reference responses

- Technical documentation

- Installation notes

- HDL core specification

- Datasheet

- Synthesis scripts

- Example application

- Netlist

- Netlist for selected FPGA family

- Sample FPGA project

- Technical documentation

- HDL core specification

- Datasheet

- Technical support

- IP Core implementation

- 3 months maintenance

- Delivery of the IP Core and documentation updates

- Phone & email support

- Design consulting

# **BLOCK DIAGRAM**

#### **PERFORMANCE**

The following table gives a survey about the Core area and performance in **ASIC** devices (all key features included):

| Configuration type | Gates | Technology |

|--------------------|-------|------------|

| Single audio block | 2100  | 0.09 μm    |

| Double audio block | 4400  | 0.09 μm    |

| Triple audio block | 6200  | 0.09 μm    |

| Quad audio block   | 7900  | 0.09 μm    |

#### **LICENSING**

Comprehensible and clearly defined licensing methods without royalty-per-chip fees make use of our IP Cores easy and simple.

- **Single-Site license option** dedicated to small and middle sized companies which run their business at one place.

- **Multi-Site license option** dedicated to corporate customers which operate at several locations. The licensed product can be used at selected company branches.

In all cases the number of IP Core instantiations within a project and the number of manufactured chips are unlimited. There are no restrictions regarding the time of use.

There are two formats of the delivered IP Core that you can choose from:

- VHDL or Verilog RTL synthesizable source code (called HDL Source code)

- FPGA EDIF/NGO/NGD/QXP/VQM (called Netlist)

HDL Source code is suitable for ASIC and FPGA projects. The Netlist license is intended for FPGA projects only.

#### CONTACT

**Digital Core Design Headquarters:** Wroclawska 94, 41-902 Bytom, POLAND

E-mail: info@dcd.pl tel.: 0048 32 282 82 66 fax: 0048 32 282 74 37 **Distributors:**

Please check: dcd.pl/contact-us/